2.2 Verilog 数值表示

数值种类 Verilog HDL 有下列四种基本的值来表示硬件电路中的电平逻辑: 0:逻辑 0 或 "假" 1:逻辑 1 或 "真" x 或 X:未知 z 或 Z:...

2.1 Verilog 基础语法

格式 Verilog 是区分大小写的。 格式自由,可以在一行内编写,也可跨多行编写。 每个语句必须以分号为结束符。空白符(换行、制表、空格)...

1.4 Verilog 设计方法

设计方法 Verilog 的设计多采用自上而下的设计方法(top-down)。即先定义顶层模块功能,进而分析要构成顶层模块的必要子模块;然后进一步对...

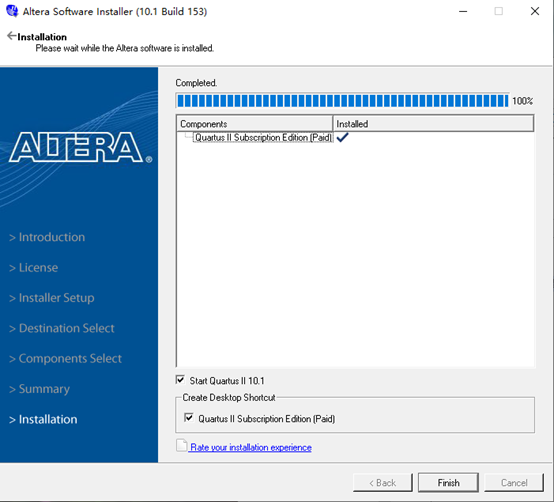

1.3 Verilog 环境搭建

学习 Verilog 做仿真时,可选择不同仿真环境。FPGA 开发环境有 Xilinx 公司的 ISE(目前已停止更新),VIVADO;因特尔公司的 Quartus II;ASIC...

1.2 Verilog 简介

Verilog 具有很强的电路描述与建模能力,能从多个层次对数字系统进行描述和建模。因此,在简化硬件设计任务、提高设计效率与可靠性、语言易读...

1.1 Verilog 教程

Verilog HDL(简称 Verilog )是一种硬件描述语言,用于数字电路的系统设计。可对算法级、门级、开关级等多种抽象设计层次进行建模。 Verilog...