4.5 Verilog 条件语句

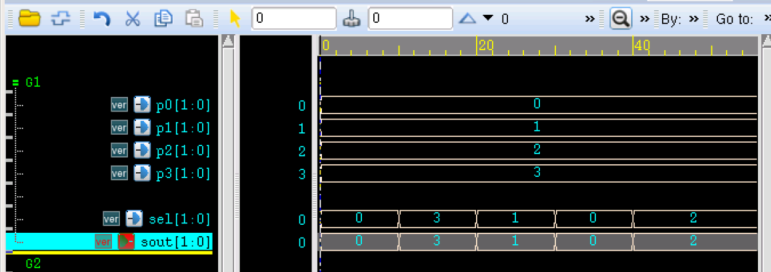

关键词:if,选择器 条件语句 条件(if)语句用于控制执行语句要根据条件判断来确定是否执行。 条件语句用关键字 if 和 else 来声明,条件...

4.4 Verilog 语句块

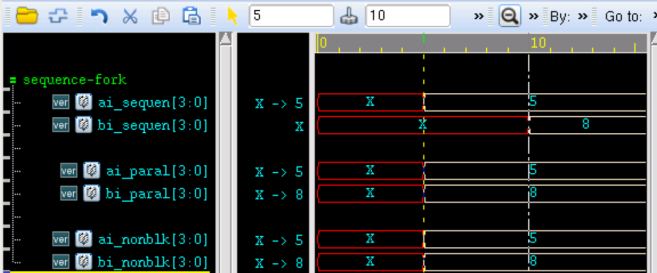

关键词:顺序块,并行块,嵌套块,命名块,disable Verilog 语句块提供了将两条或更多条语句组成语法结构上相当于一条一句的机制。主要包括两...

4.3 Verilog 时序控制

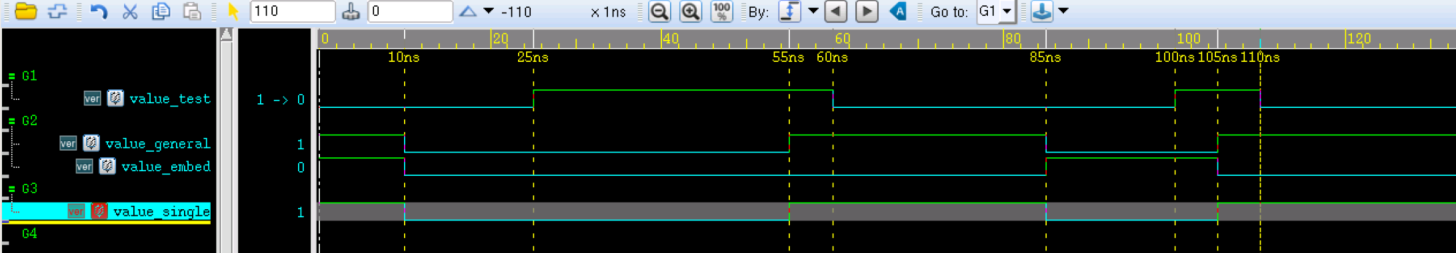

关键词:时延控制,事件触发,边沿触发,电平触发 Verilog 提供了 2 大类时序控制方法:时延控制和事件控制。事件控制主要分为边沿触发事件控...

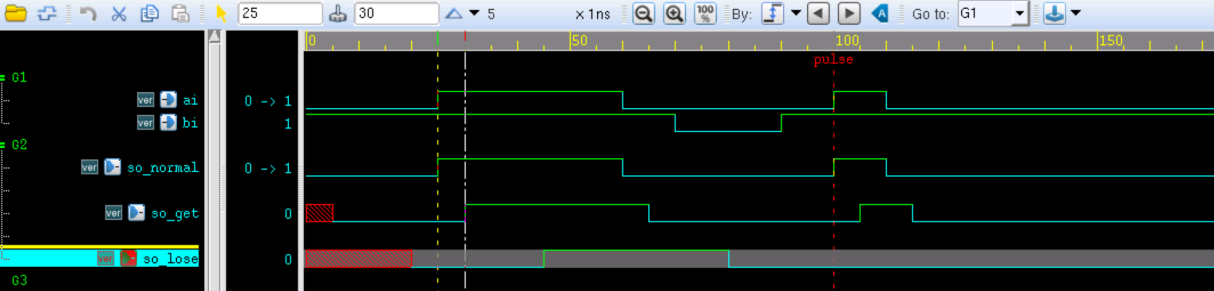

4.2 Verilog 过程赋值

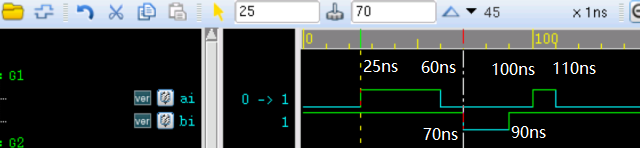

关键词:阻塞赋值,非阻塞赋值,并行 过程性赋值是在 initial 或 always 语句块里的赋值,赋值对象是寄存器、整数、实数等类型。 这些变量在...

4.1 Verilog 过程结构

关键词:initial, always 过程结构语句有 2 种,initial 与 always 语句。它们是行为级建模的 2 种基本语句。 一个模块中可以包含多个 init...

2.5 Verilog 编译指令

以反引号 ` 开始的某些标识符是 Verilog 系统编译指令。编译指令为 Verilog 代码的撰写、编译、调试等提供了极大的便利。 下面介绍下完整的 8...

3.2 Verilog 时延

关键词:时延, 惯性时延 连续赋值延时语句中的延时,用于控制任意操作数发生变化到语句左端赋予新值之间的时间延时。 时延一般是不可综合...

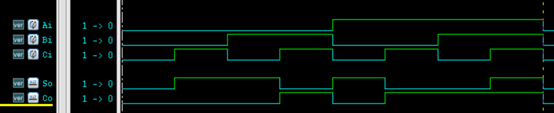

3.1 Verilog 连续赋值

关键词:assign, 全加器 连续赋值语句是 Verilog 数据流建模的基本语句,用于对 wire 型变量进行赋值。:格式如下 assign LHS_target =...

2.4 Verilog 表达式

表达式 表达式由操作符和操作数构成,其目的是根据操作符的意义得到一个计算结果。表达式可以在出现数值的任何地方使用。例如: 实例 a^b...

2.3 Verilog 数据类型

Verilog 最常用的 2 种数据类型就是线网(wire)与寄存器(reg),其余类型可以理解为这两种数据类型的扩展或辅助。 线网(wire) wir...