6.4 Verilog 竞争与冒险

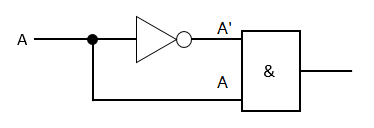

关键字:竞争,冒险,书写规范 产生原因 数字电路中,信号传输与状态变换时都会有一定的延时。 在组合逻辑电路中,不同路径的输入信号变化...

6.3 Verilog 状态机

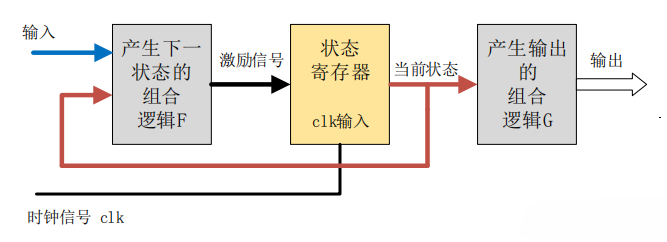

关键词:状态机,售卖机 有限状态机(Finite-State Machine,FSM),简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数...

6.2 Verilog 任务

关键词:任务 任务与函数的区别 和函数一样,任务(task)可以用来描述共同的代码段,并在模块内任意位置被调用,让代码更加的直观易读。函...

6.1 Verilog 函数

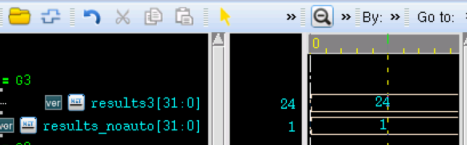

关键词:函数,大小端转换,数码管译码 在 Verilog 中,可以利用任务(关键字为 task)或函数(关键字为 function),将重复性的行为级设计进...

5.3 Verilog 带参数例化

关键词: defparam,参数,例化,ram 当一个模块被另一个模块引用例化时,高层模块可以对低层模块的参数值进行改写。这样就允许在编译时将不...

5.2 Verilog 模块例化

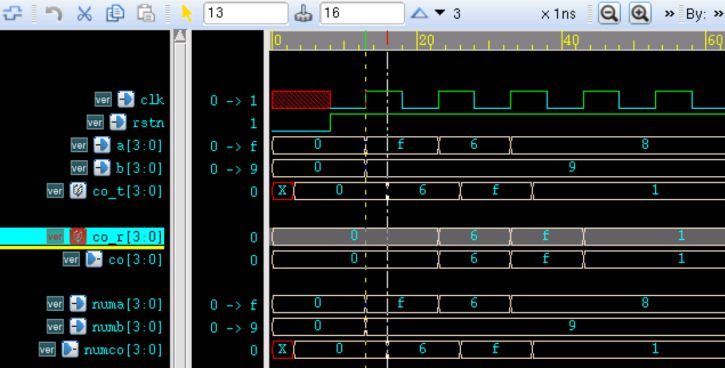

关键字:例化,generate,全加器,层次访问 在一个模块中引用另一个模块,对其端口进行相关连接,叫做模块例化。模块例化建立了描述的层次。...

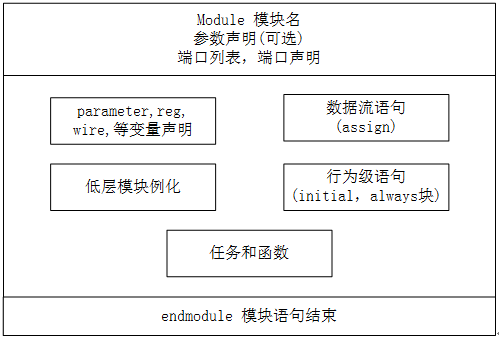

5.1 Verilog 模块与端口

关键词:模块,端口,双向端口,PAD 结构建模方式有 3 类描述语句: Gate(门级)例化语句,UDP (用户定义原语)例化语句和 module (模块) 例...

4.8 Verilog 过程连续赋值

关键词:deassign,force,release 过程连续赋值是过程赋值的一种。这种赋值语句能够替换其他所有 wire 或 reg 的赋值,改写了 wire 或 reg ...

4.7 Verilog 循环语句

关键词:while, for, repeat, forever Verilog 循环语句有 4 种类型,分别是 while,for,repeat,和 forever 循环。循环语句只能在 always ...

4.6 Verilog 多路分支语句

关键词:case,选择器 case 语句是一种多路条件分支的形式,可以解决 if 语句中有多个条件选项时使用不方便的问题。 case 语句 case 语...