编写代码前,在系统与架构层次上制定完善低功耗方案,可以节省 50% 以上的功耗。此类低功耗设计和代码描述基本没有关系,往往由系统和架构人员进行设计。此类人员需要较丰富的硬件经验,能对系统有一个良好的整体把握。方案制定后,再交予功能设计人员(例如 IC 前端设计、FPGA 工程师等)实现。

多电压技术

一般来说,电压越低,功耗越低,但是性能往往会越差。综合功耗与性能的考虑,可以对不同的模块采用不同的电压设计。

多电压技术主要有 3 种:

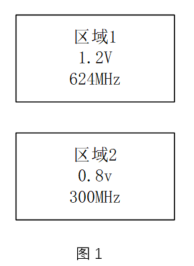

- 1、各电压区域有固定的电压,如图 1 所示。

- 2、各电压区域有固定的电压,电压的选择由软件控制,如图 2 所示。

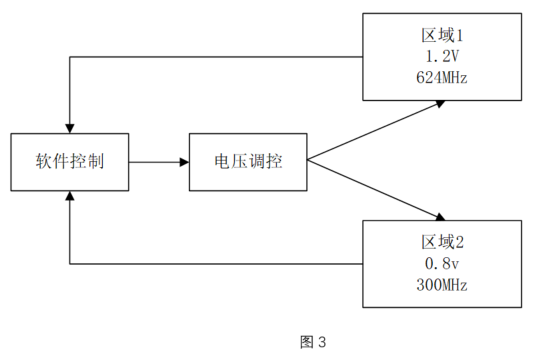

- 3、自适应的方式,各区域电压可变,电压选择也是由软件控制,又称为动态电压条件,如图 3 所示。

一般来说,供电电压越大,电路延迟越小,性能越高。例如,芯片的处理器核、存储器一般需要较高的性能,所以可以采用较高的电压方案。其他外部设计,可以采用较小的电压方案,来降低功耗。

系统时钟分配

一般来说,频率越高,性能越好,但功耗越大。通过合理的时钟分配,也能有效的降低功耗,一般有以下几种方法:

1、通过时钟分频,各模块采用合理的工作时钟

一般 CPU 总线需要较高的时钟来满足较高的设计需求,而 uart,spi 等外设工作频率不会很高。如果设计中一视同仁都采用较高的工作频率,显然会增加无端的功耗。

将高速时钟进行一定的分频,分别赋予不同的模块。在满足工作性能的条件下看,采用较低的工作时钟频率,可以有效减少功耗。

2、加入多种低功耗工作模式

设计中加入多种低功耗时钟分配方案,人为的来选择一种工作模式,可以降低功耗。各种低功耗模式设计可以参考如下:

| 模式 | 说明 |

|---|---|

| Normal | 主时钟使用较高频率的锁相环时钟,送入到设计电路中 |

| Slow | 主时钟使用较低的本地时钟 |

| Low-Power | 总线时钟关闭,只保留一些外设的工作时钟 |

| Sleep | 时钟全部关闭,全设计进入睡眠状态 |

3、自适应选择工作频率

和多电压技术的电压自适应调整类似,根据当前的工作状态来选择合适的工作频率,也可以降低功耗。

例如电脑在处理一些简单的文档时,可以选择相对较低的工作频率;而电脑在处理一些视频渲染工作时,则需要相对较高的工作频率。

工作频率和电压的动态调整,往往是低功耗设计中同时需要的策略。

软硬件划分

系统中的功耗都是硬件单元消耗的。在设计过程中,系统的功能可以用硬件实现,也可以使用软件实现。

系统设计者根据设计规范和自身经验对系统性能进行推测(仿真建模),决定哪一部分使用硬件来实现,哪一部分使用软件来实现,从而达到性能和功耗的最佳平衡。例如一些参数的计算,软件计算完成后直接输入给硬件,是比较合理的设计。

总之,软硬件划分可以很大程度上降低功耗,这是系统设计者需要慎重考虑的。

ip 或单元库选择

现在很多设计也依赖于 IP 的集成。选择 IP 时,在满足工作性能的条件下,也需要合理的选择功耗相对较低的 IP 。

设计中使用到的标准单元库,虽然实现的逻辑功能相同,但也会因为工艺库的不同具有不同的电压阈值。

LVT(Low Voltage Threshold),阈值电压低,饱和电流小,所以此类单元库具有更高的速度和更大的泄漏电流。

HVT(High Voltage Threshold)单元漏电流小,但速度较慢。

SVT/RVT(Standard/Regular Voltage Threshold) 的性能介于 LVT 与 HVT 之间。

所以选用标准单元库的时候,需要综合速度和功耗两个方面来考虑。

例如,可以在关键路径使用 LVT 单元,在非关键路径使用 HVT 单元。

其他

还有一些其他可以减少功耗的系统方法,如下一些举例:

- 合理选择算法,例如使用查找表的方法代替乘除运算,有时可以减少一些功耗。

- 利用握手信号完成异步设计,省去全局时钟,也可以减少功耗。

- ……