5.2 Verilog 模块例化

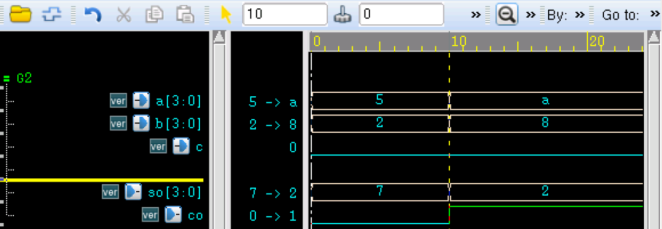

关键字:例化,generate,全加器,层次访问 在一个模块中引用另一个模块,对其端口进行相关连接,叫做模块例化。模块例化建立了描述的层次。...

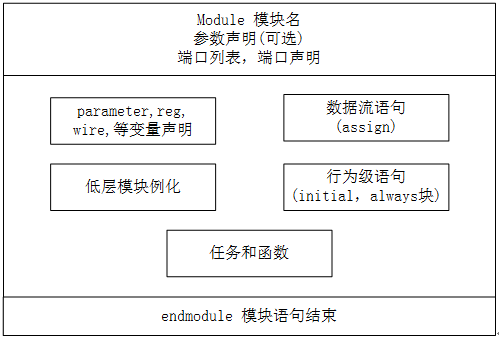

5.1 Verilog 模块与端口

关键词:模块,端口,双向端口,PAD 结构建模方式有 3 类描述语句: Gate(门级)例化语句,UDP (用户定义原语)例化语句和 module (模块) 例...

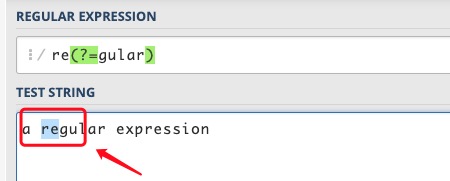

正则表达式的先行断言(lookahead)和后行断言(lookbehind)

正则表达式的先行断言和后行断言一共有 4 种形式: (?=pattern) 零宽正向先行断言(zero-width positive lookahead assertion) (?!patter...

4.8 Verilog 过程连续赋值

关键词:deassign,force,release 过程连续赋值是过程赋值的一种。这种赋值语句能够替换其他所有 wire 或 reg 的赋值,改写了 wire 或 reg ...

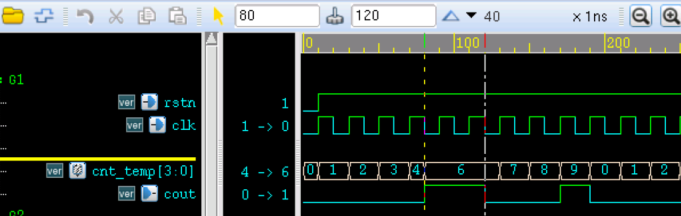

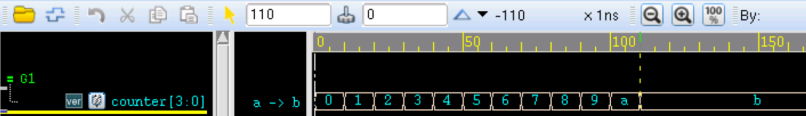

4.7 Verilog 循环语句

关键词:while, for, repeat, forever Verilog 循环语句有 4 种类型,分别是 while,for,repeat,和 forever 循环。循环语句只能在 always ...

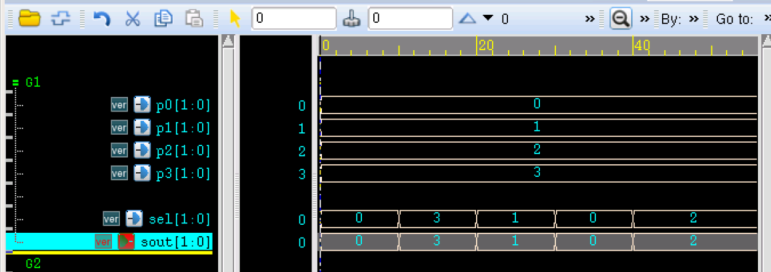

4.6 Verilog 多路分支语句

关键词:case,选择器 case 语句是一种多路条件分支的形式,可以解决 if 语句中有多个条件选项时使用不方便的问题。 case 语句 case 语...

4.5 Verilog 条件语句

关键词:if,选择器 条件语句 条件(if)语句用于控制执行语句要根据条件判断来确定是否执行。 条件语句用关键字 if 和 else 来声明,条件...

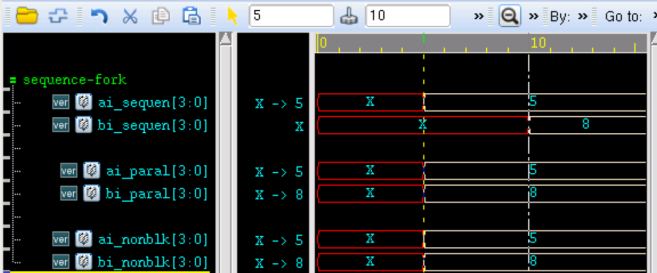

4.4 Verilog 语句块

关键词:顺序块,并行块,嵌套块,命名块,disable Verilog 语句块提供了将两条或更多条语句组成语法结构上相当于一条一句的机制。主要包括两...

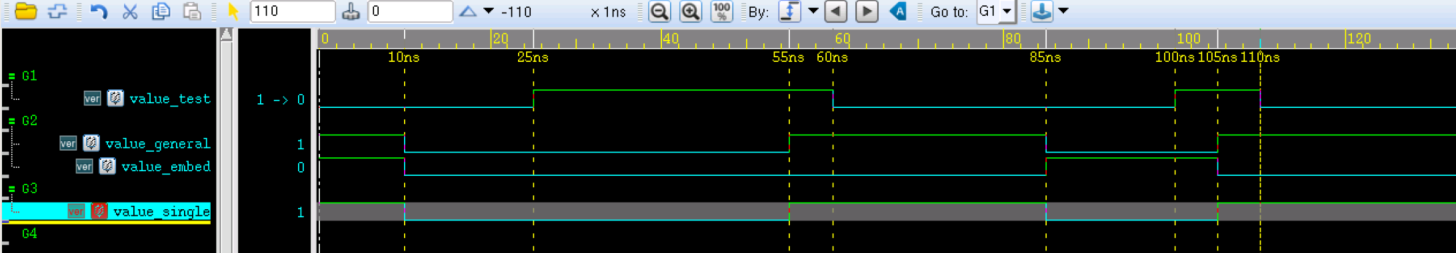

4.3 Verilog 时序控制

关键词:时延控制,事件触发,边沿触发,电平触发 Verilog 提供了 2 大类时序控制方法:时延控制和事件控制。事件控制主要分为边沿触发事件控...

4.2 Verilog 过程赋值

关键词:阻塞赋值,非阻塞赋值,并行 过程性赋值是在 initial 或 always 语句块里的赋值,赋值对象是寄存器、整数、实数等类型。 这些变量在...